### International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

# Design and Implementation of CLA Using Reversible Logic Gates

S.T.Suria, M.Jenath (\*)

Department of Electronics and Communication Engineering, Adhiparasakthi Engineering College, Melmaruvathur, Chennai, India

ABSTRACT: Reversible logic is a popular concept in energy efficient computations and this will be the demand for upcoming future computing technologies. Reversible logic is emerging as an important research area and it will be having wide applications in many fields such as optical information processing, quantum computing and Low power CMOS design. The main purpose of designing reversible logic is to decrease quantum cost, depth of the circuits and the number of garbage outputs. Reversible are circuits (gates) that have one to one mapping between vectors of inputs and outputs; thus the vector of inputstates can be always reconstructed from the vector of output states. Reversible logic is playing a significant role in quantum computing as quantum operations are unitary in nature. Quantum computer performs computation at an atomic level; thereby doing high performance computations beyond the limits of the conventional computing systems. Reversible arithmetic units such as adders, subtractors, multipliers form the essential component of a quantum computing system. Among the adder designs, carry look-ahead is widely used in high performance computing due to its O (log n) depth. In this work, we present improved designs of both in-place and out-of-place reversible carry look-ahead adder proposed. The proposed designs utilize the properties of the Reversible Peres gate are optimize the logic depth, quantum cost and gate count compared to the existing designs proposed to both the improved designs assume no input carry (C0=0). While the first approach makes use of ancilla bits to store the sum outputs, the second approach stores the sum outputs in one of the input locations.

KEYWORDS: Reversible logic gates, Reduced garbage output, Quantum cost, Low power design, Carry look-ahead adder, Peres gate, Ancilla bits.

#### I. INTRODUCTION

The demand for implementing ultralow-power digital systems in many modern applications, such as mobile systems, sensor networks, and implanted biomedical systems, has increased the importance of designing logic circuits in subthreshold regime. These emerging applications have low energy as the primary concern instead of performance, with the eventual goal of harvesting energy from the environment.

The heat dissipated in the circuit will gradually decrease the performance and also life span of the circuit or device. In order to overcome these types of problems, we require low power consumption and less dissipation components in the circuit. He proposed two conditions of reversibility. 1<sup>st</sup>condition: For any device to be reversible if its input and output will be uniquely retrievable from each other called logical reversibility. 2<sup>nd</sup>condition: A device can run actually backwards then it is called physically reversible.

The reversible circuits are those in which reversible logic gates are basic building blocks and there is no energy loss. The reversible logic gates will be having n-input and n-output i.e. equal number of input and equal number of output, and also with one-to-one mapping i.e. inputs can be uniquely recovered from the outputs. Reversible logic supports the process of running the system both forward and backward.

Copyright to IJIRSET DOI:10.15680/IJIRSET.2016.0505307 8777

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

#### II. REVERSIBLE LOGIC

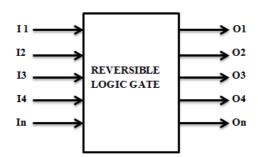

The reversible logic gate will generate unique output vector from unique input vector or vice-versa. In reversible logic, Input vector is  $Iv=(I_1,I_2,I_3...In)$  and Output vector is  $Iv=(O_1,O_2,O_3.....On)$ , For each particular vector  $iv=(O_1,O_2,O_3.....On)$ , For each particular vector  $iv=(O_1,O_2,O_3.....On)$

Fig.1shows a general reversible gate; the gate will be having k inputs and k outputs and it is called ak\*k reversible gate. In reversible gates, fan-out are not permitted. No feedback paths are allowed i.e. circuit is acyclic. Some important factors are Garbage output, constant input etc. Garbage output is the un-utilized output from the reversible gate, very much essential to achieve reversibility and it must be not used for further computation. Constant inputs are those that will be added to k\*k function to make it reversible. For an optimized reversible circuit, the number of garbage outputs, the number of constant inputs and the number of reversible gates used should be minimum.

Fig.1.General reversible gate

In the design of reversible logic circuits the following points must be considered to achieve an optimized circuit. They are:

- Fan-out is not allowed.

- Loop or feedback is not permitted.

- Garbage outputs should be minimum.

- Minimum delay.

- Minimum quantum cost.

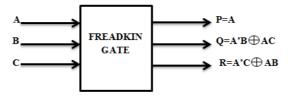

### FREDKIN GATE (FRG)

The input vector is I(A, B, C) and the output vector is O(P, Q, R). The output is defined by P=A, Q=A'B ^ AC and R=A'C ^ AB. The Quantum cost of a Fredkin gate is 5.

Fig.2:3\*3 Fredkin gate.

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

### TRUTH TABLE OF PARITY PRESERVING FREDKIN GATE

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| A     | В | C | P      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 0 | 0 |  |

| 1     | 0 | 1 | 1      | 1 | 0 |  |

| 1     | 1 | 0 | 1      | 0 | 1 |  |

| 1     | 1 | 1 | 1      | 1 | 1 |  |

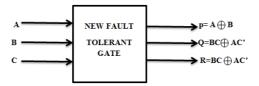

### **NEW FAULT TOLERANT GATE (NFT)**

The NFT gate is a 3\*3 Reversible gate with three inputs and three outputs[8]. The input vector is I(A, B, C) and the output vector is O(P, Q, R). The output is defined by P=A^B, Q=BC^AC', R=BC^AC'and is shown in the Fig. 4.The Quantum cost of a NFT gate is 5.

Fig 3.3\*3 NFT gate.

### TRUTH TABLE OF PARITY PRESERVINGNFT GATE

| Input |   |   | Output |   |   |  |

|-------|---|---|--------|---|---|--|

| A     | В | C | P      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 1 | 0 |  |

| 0     | 1 | 0 | 1      | 0 | 0 |  |

| 0     | 1 | 1 | 1      | 0 | 1 |  |

| 1     | 0 | 0 | 1      | 1 | 1 |  |

| 1     | 0 | 1 | 1      | 1 | 0 |  |

| 1     | 1 | 0 | 0      | 1 | 1 |  |

| 1     | 1 | 1 | 0      | 0 | 1 |  |

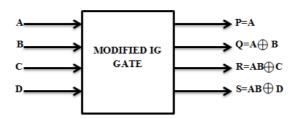

### **MODIFIED IG GATE (MIG)**

The MIG gate is a 4\*4 Reversible gate with four inputs and four outputs[8]. The input vector is I(A, B, C, D) and the output vector is O(P, Q, R, S). The output is defined by P=A, Q=A^B, R=(A&B) ^ C, S=(A&B) ^ D and is shown in the Fig. 5. The Quantum cost of a MIG gate is 7.

# International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

Fig 4.4\*4 MIG gate.

### TRUTH TABLE OF PARITY PRESERVING MIG GATE

| Input |   |   |   | Output |   |   |   |

|-------|---|---|---|--------|---|---|---|

| A     | В | C | D | P      | Q | R | S |

| 0     | 0 | 0 | 0 | 0      | 0 | 0 | 0 |

| 0     | 0 | 0 | 1 | 0      | 0 | 0 | 1 |

| 0     | 0 | 1 | 0 | 0      | 0 | 1 | 0 |

| 0     | 0 | 1 | 1 | 0      | 0 | 1 | 1 |

| 0     | 1 | 0 | 0 | 0      | 1 | 0 | 0 |

| 0     | 1 | 0 | 1 | 0      | 1 | 0 | 1 |

| 0     | 1 | 1 | 0 | 0      | 1 | 1 | 0 |

| 0     | 1 | 1 | 1 | 0      | 1 | 1 | 1 |

| 1     | 0 | 0 | 0 | 1      | 1 | 0 | 1 |

| 1     | 0 | 0 | 1 | 1      | 1 | 0 | 0 |

| 1     | 0 | 1 | 0 | 1      | 1 | 1 | 1 |

| 1     | 0 | 1 | 1 | 1      | 1 | 1 | 0 |

| 1     | 1 | 0 | 0 | 1      | 0 | 1 | 0 |

| 1     | 1 | 0 | 1 | 1      | 0 | 1 | 1 |

| 1     | 1 | 1 | 0 | 1      | 0 | 0 | 0 |

| 1     | 1 | 1 | 1 | 1      | 0 | 0 | 1 |

| INPUT |   |   | OUTPUT |   |   |  |

|-------|---|---|--------|---|---|--|

| A     | В | С | P      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 0 | 0 |  |

| 1     | 0 | 1 | 1      | 0 | 1 |  |

| 1     | 1 | 0 | 1      | 1 | 1 |  |

| 1     | 1 | 1 | 1      | 1 | 0 |  |

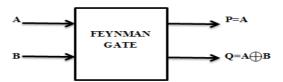

### **FEYNMAN GATE**

Feynman gate is a 2x2 reversible gate. The input vector is I(A,B) and the output vector is O(P,Q). The output defined by P=A,Q=A AB. Quantum cost of a Feynman gate is 1. Feynman gate can be used as copying gate.

Fig 5.2\*2 Feynman gate

### International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

### TRUTH TABLE OF FEYNMAN GATE

| INP | UT | OUTPUT |   |  |

|-----|----|--------|---|--|

| A   | В  | P      | Q |  |

| 0   | 0  | 0      | 0 |  |

| 0   | 1  | 0      | 1 |  |

| 1   | 0  | 1      | 1 |  |

| 1   | 1  | 1      | 0 |  |

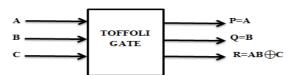

### **TOFFOLI GATE**

Toffoli gate is 3x3 reversible gate. The input vector is I(A,B,C) and the output vector is O(P,Q,R). The outputs are defined by P=A,Q=B,R=ABC. Quantum cost of a TOFFOLI gate is 5.

Fig 6: 3\*3 Toffoli gate

### PERES GATE

Peres gate is 3x3 reversible gate. The input vector is I(A,B,C) and the output vector is O(P,R,S). The output is defined by P=A,Q=A+B and R=ABC. Quantum cost of a Peres gate is 4.

Fig 7: Peres gate

### TRUTH TABLE OF PERES GATE:

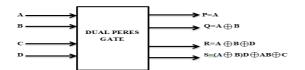

### **DOUBLE PERES GATE (DPG)**

DPG gate is 4x4 reversible gate. The input vector is I(A,B,C,D) and the output vector is O(P,Q,R,S). The output is  $P=A,Q=A \oplus B,R=A \oplus B \oplus D$  and  $S=(A \oplus B)D \oplus AB \oplus C$ . Quantum cost of DPG gate is 6.It can work singly as Reversible full adder with C=0 and D=C in.

| INPUT |   |   | OUTPUT |   |   |  |

|-------|---|---|--------|---|---|--|

| A     | В | С | P      | Q | R |  |

| 0     | 0 | 0 | 0      | 0 | 0 |  |

| 0     | 0 | 1 | 0      | 0 | 1 |  |

| 0     | 1 | 0 | 0      | 1 | 0 |  |

| 0     | 1 | 1 | 0      | 1 | 1 |  |

| 1     | 0 | 0 | 1      | 1 | 0 |  |

| 1     | 0 | 1 | 1      | 1 | 1 |  |

| 1     | 1 | 0 | 1      | 0 | 1 |  |

| 1     | 1 | 1 | 1      | 0 | 0 |  |

Fig 8.4\*4 dual peres gate

# International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

### TRUTH TABLE OF DUAL PERES GATE

|   | INF | UT |   | OUTPUT |   |   |   |

|---|-----|----|---|--------|---|---|---|

| A | В   | С  | D | P      | Q | R | S |

| 0 | 0   | 0  | 0 | 0      | 0 | 0 | 0 |

| 0 | 0   | 0  | 1 | 0      | 0 | 0 | 1 |

| 0 | 0   | 1  | 0 | 0      | 0 | 1 | 0 |

| 0 | 0   | 1  | 1 | 0      | 0 | 1 | 1 |

| 0 | 1   | 0  | 0 | 0      | 1 | 1 | 0 |

| 0 | 1   | 0  | 1 | 0      | 1 | 1 | 1 |

| 0 | 1   | 1  | 0 | 0      | 1 | 0 | 1 |

| 0 | 1   | 1  | 1 | 0      | 1 | 0 | 0 |

| 1 | 0   | 0  | 0 | 1      | 1 | 1 | 0 |

| 1 | 0   | 0  | 1 | 1      | 1 | 1 | 1 |

| 1 | 0   | 1  | 0 | 1      | 1 | 0 | 1 |

| 1 | 0   | 1  | 1 | 1      | 1 | 0 | 0 |

| 1 | 1   | 0  | 0 | 1      | 0 | 0 | 1 |

| 1 | 1   | 0  | 1 | 1      | 0 | 0 | 0 |

| 1 | 1   | 1  | 0 | 1      | 0 | 1 | 1 |

| 1 | 1   | 1  | 1 | 1      | 0 | 1 | 0 |

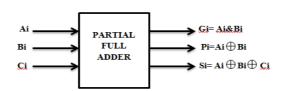

### CARRY LOOK-AHEAD ADDER

Carry look-ahead adder are fastest adder of all adders because it calculates the carry bits before the summation. Carry look-ahead adder actually determines the carry bit by two modules first is "generate a carry" and second is "propagate a carry". Carry signal will be generated in two conditions. When both bits Ai and Bi are equal to 1 or when carry-in is 1 and Ai or Bi is 1.

Carry propagation (Pi) and Carry generation (Gi) are

Pi = Ai ⊕ Bi

Gi = Ai Bi

Sum signal can be calculated as follows:

$Si = Ai \oplus Bi \oplus Ci = Pi \oplus Ci$

Carry signal can be calculated as

Ci+1 = Gi ⊕ Pi Ci

Applying this to a 4-bit adder ,we have:

$C1 = G0 \oplus P0C0$

$C2 = G1 \oplus P1C1 = G1 \oplus P1(G0 \oplus P0C0)$

$C3 = G2 \oplus P2C2 = G2 \oplus P2(G1 \oplus P1C1)$

Partial Full Adder (PFA): This adder generates Gi, Pi and Si.

$Pi = Ai \bigoplus Bi$ ,

Gi= Ai.Bi,

Si= Ai⊕Bi⊕Ci

Fig 9.Partial full adder

# International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

### REVERSIBLE LOGIC CARRY LOOK AHEAD ADDER

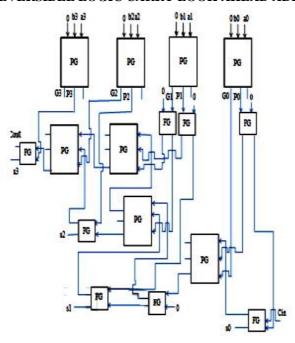

Fig.10.Architecture of proposed 4-bit reversible carry look-ahead adder

### III. RESULT

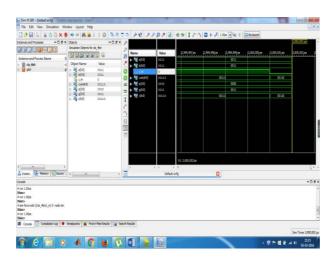

### SIMULATION OUTPUT

Fig.11.simulation output

# International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

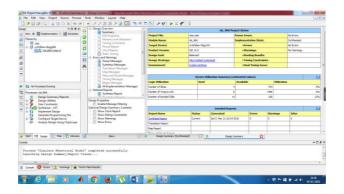

### **AREA**

Fig.12.performance of area report

### CALCULATE DELAY

Fig.13.performance of delay

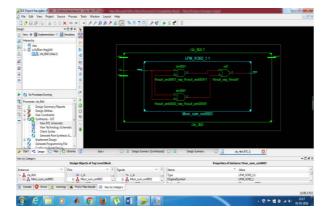

### **RTL DIAGRAM**

Fig.14.Performance of RTL diagram

Copyright to IJIRSET DOI:10.15680/IJIRSET.2016.0505307 8784

# International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

### PROCESS OF TECHNOLOGY

Fig.15.Technology diagram

### POWER CONSUMPTION

Fig.16.power consumption diagram

### IV. CONCLUSION

Reversible logic gates are used to Reduced the power consumption, Minimum delay ,Garbage outputs should be minimum, Minimum quantum cost, performance is high due to area is reduced.

### REFERENCES

<sup>[1]</sup> Ashima Malhotra, Charanjit Singh, Amandeep Singh, "Efficient Design of Reversible Multiplexers with Low Quantum Cost and Power Consumption", International Journal of Emerging Technology and Advanced Engineering, Volume 4, Issue 7, July 2014.

<sup>[2]</sup> Ashima Malhotra, Charanjit Singh, Amandeep Singh, "Efficient Design of Reversible Multiplexers with Low Quantum Cost", International Journal of Engineering Research and Applications, Volume 4, Issue 7, July 2014.

### International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 5, May 2016

- [3] B.Raghu Kanth, "A Distinguish between reversible and conventional logic gates", International Journal of Engineering Research and Application, Vol. No.2, Issue No.2, pp.148-151,2012.

- [4] Lafifa Jamal, Md.Shamsujjoha,Hafiz Md.Hasan Babu, "Design of Optimal Reversible Carry Look-ahead Adder with Optimal Garbage and Quantum Cost", International Journal of Engineering and Technology, Vol. No. 2, 2012.

- [5] Prashant.R.Yelekar, "Introduction to reversible logic gates and its application", 2<sup>nd</sup> National Conference on Information and communication Technology, 2011.

- [6] Y. Cao, Predictive Technology Model for Robust Nanoelectronic Design. New York, NY, USA: Springer-Verlag, 2011.

- [7] D.Michael Miller and Zahra Sasanian, "Lowering the quantum gate cost of reversible circuits", IEEE, 2010.

- [8] J. Kwong, Y. K. Ramadass, N. Verma, and A. P. Chandrakasan, "A 65 nm sub-Vt microcontroller with integrated SRAM and switched capacitor DC-DC converter," *IEEE J. Solid-State Circuits*, vol. 44, no. 1, pp. 115–126, Jan. 2009.

- [9] N. S. S. Reddy, M. Satyam, and K. L. Kishore, "Cascadable adiabatic logic circuits for low-power applications," *IET Circuits, Devices Syst.*, vol. 2, no. 6, pp. 518–526, Dec. 2008.